测试姿势不过关,结果偏差得加班!

发布时间:2023-09-18 11:08

作者:797966金沙娱场城高速先生自媒体成员 黄刚

通常情况下,我们都认为测试是一种比较有效而且准确的方法,但是当测试结果出乎我们预料之后,我们该如何去判断和排查呢?本期文章给大家分享下这个案例哈!

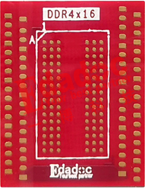

这是一个利用高速先生实验室示波器来测试DDR4模块的测试案例,客户在他们自己功能测试完成之后,还想找我们来测试下信号质量和看看时序。听说到我们这边有示波器以及对应的DDR测试套件后,就把他们自己的产品板带过来我们这边,让我们开展这个测试项目。测试情况大概是这样子的:该DDR4信号速率1600Mbps,一拖四的拓扑,这个项目用上了高速先生研发的interposer板,把需要测试的颗粒进行riser板抬高后利用interposer板去做焊接,从而就有了可以测试的测试点了!大家还记得interposer夹具板的样子吗?下图就是我们高速先生研发的interposer夹具板哈!

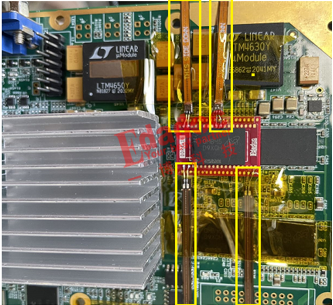

经过一顿操作,我们就通过测试排线在焊接好的interposer板引出测试的信号,分别是一对CLK,一根地址信号,一对DQS信号和一根DQ信号,整个测试场景就像下面这样哈!

从我们搭建的测试场景来看,高速先生还是比较用心的哈,不仅很规整的把4对测试排线焊在测试点上去,另外还有绝缘胶纸分隔开来避免短路,并防止外界环境对测试排线的干扰。

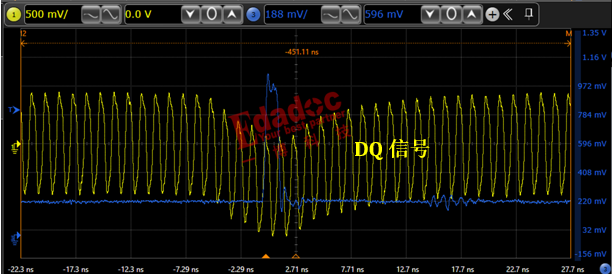

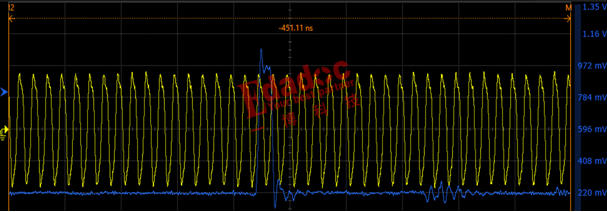

在花了不少时间完成这个搭建之后,我们就正式开始测试了。我们熟练的对示波器进行一轮设置后就准备可以观看波形了,但是当我们测试到DQS信号时,通过捕捉波形时就发现了问题!DQ总会有跑一段时间之后有一个诡异的跌落,跌落的幅度还不小,达到了200mV。

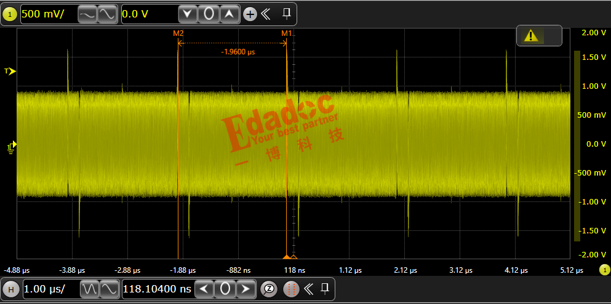

然后我们就重点关注DQS信号,并而把这个DQS的时间轴拉大,来看看更宽的时间的轴情况下这个跌落是不是有规律可言,结果发现不仅在DQS信号上看到了这个跌落,更重要的发现了这个跌落是具有周期性的,我们量测后发现周期大概在2us左右!

这个跌落肯定是我们意料之外的测试结果,最大的纹波峰峰值超过了3V,显然是受到了某个比较大的噪声源的影响。通过测量两个峰值噪声的周期为2us,可以反推出该噪声的频率为500kHz,这让我们立马想到了是不是受到电源的干扰!因为电源的开关频率一般会在1MHz以下,于是我们就去检查板子的PCB文件,发现该DQ和DQS走线旁边并没有穿过电源平面或者距离电源孔很近。感觉检查了很久PCB文件都没有发现电源和DDR信号存在明显的耦合路径,这个测试的意料结果一度使测试进程陷入了僵局。 后面正当我们都准备放弃,把排线取下来的情况,突然发现了一个很重要的点!由于我们测试的角度,上面DQS和DQ线都贴上了电源模块上,于是我们立马形成了一个新的结论,那就是会不会不是由于设计引起的,而是由于我们的排线贴在了电源模块附近导致的呢?

虽然现在不能百分百确定是不是由于这个问题导致测试的噪声引起,我们还是重新对这部分排线和电源模块采取更有效的隔离。于是我们拿出了刚到货的一个“holder”,也就是一个机器臂来解放我们的双手来帮我们更好的隔开排线和电源模块。另外为了保险,又把电源模块狠狠的物理屏蔽了一番!重新搭建之后就变成如下的样子了。

然后我们再对DQ信号进行测试,果然就发现这个噪声就没有了!

虽然这个只是在该项目测试过程中,甚至是正式测试前的一个小插曲,但是如果一开始搭建测试环境的方法有问题的话,大家都能想象,后面的测试结论都会被它带偏的!因此通过这个小小的测试案例也给大家一个启示,也就是一定要特别注重测试前的各种准备工作,保证给正式测试提供一个精确可靠的测试条件哈!