深入分析:常说的3H原则在PCB设计中的应用

发布时间:2024-07-15 15:20

“3H”这个设计经验我们一直在传颂,到底它在具体PCB设计项目中到底效果怎么样呢?话不多说,本期文章从理论到实际给大家全面分析,揭开它那神秘的面纱!

#串扰#仿真#高速#电磁场#阻抗#叠层

高速先生成员--黄刚

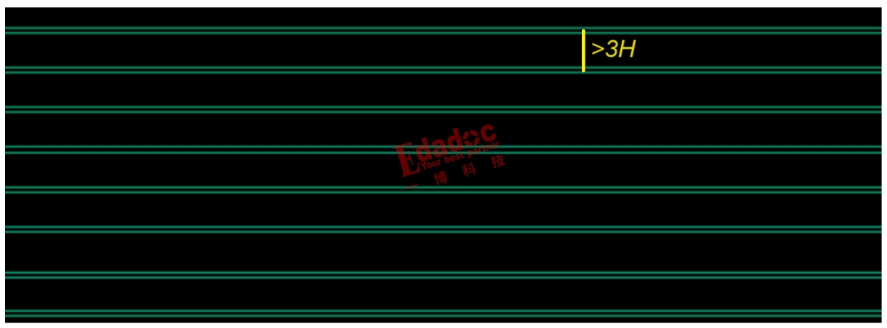

每一位刚进入PCB行业的同学,基本上头几个接触到的设计经验就肯定少不了“3H”原则。当然大家也都知道,这个原则是为了传输线之间的串扰改善而建立的规定,那就是要求传输线中心到中心的距离满足至少3H的值(也就是空气间距gap大于2H),其中H是传输线到参考平面的距离,其实也就相当于是上下层PP或者CORE的厚度了,就好像下面的样子。

当然PCB设计工程师本身只会对物理规则负责,不对电气规则负责。也就是说,SI工程师定下来“3H”原则后,PCB工程师通过叠层文件知道了H的数值后,然后在组内的高速差分线应用上去就好了。空间紧张的满足“3H”,空间不紧张的拉开到“5H”,甚至是惊人的“7H”!总之,PCB工程师只管在PCB版图上实现就完事了。

这不有一天,公司内一群好学的PCB工程师同事找到了Chris,想知道到底“3H”原则是不是就一定能让高速信号之间的串扰变得很小了,有没有必要做成“5H”甚至“7H”,总之就是,他们想让Chris把物理规则量化成电气规则。面对同事的“软磨硬泡”,行呗,那就以他们手头上的这个25Gbps的高速项目为例给他们说道说道。

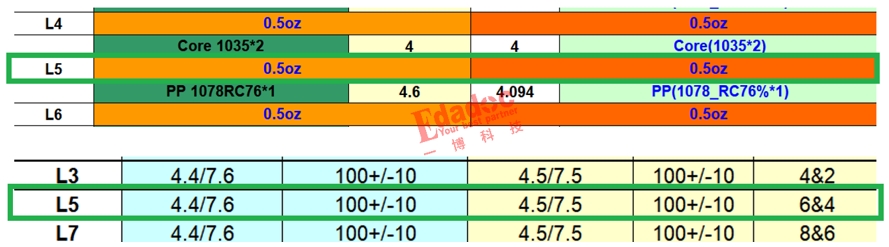

Chris先打开他们设计文件的叠层,高速线走了很多个内层,结构线宽都相同。以L5层高速线为例,上面的core厚度是4mil,下面的PP也差不多4mil。然后按照100欧姆阻抗控制的话,线宽为4.5mil,线间距为7.5mil,如下所示:

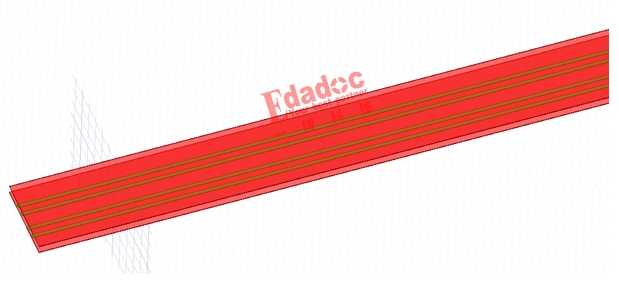

那我们把L5层的走线提取到3D模型中去,通过仿真来验证所谓的“3H”原则。模型就是下面这样了。

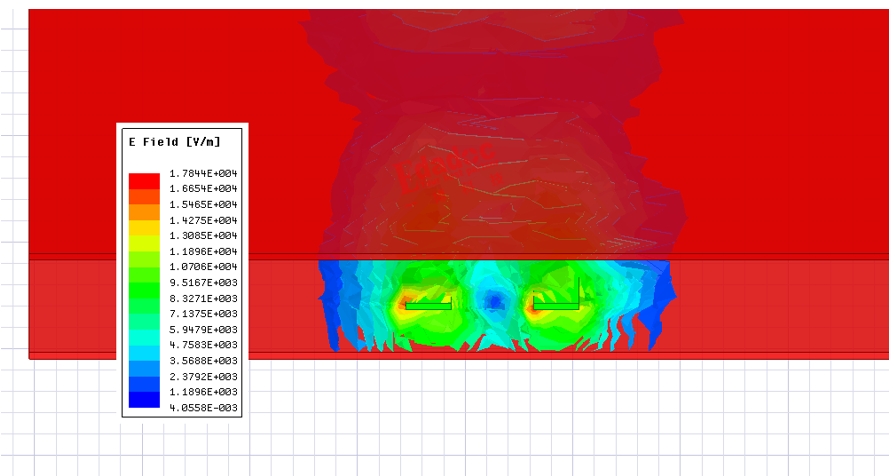

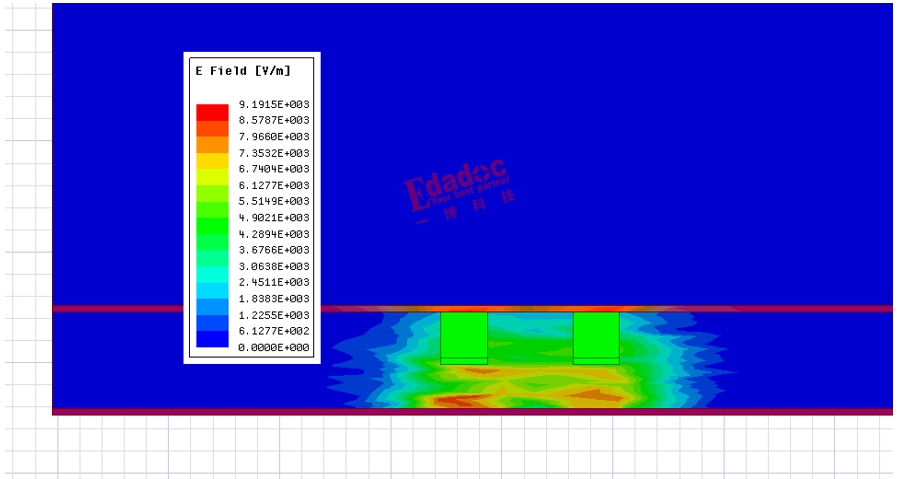

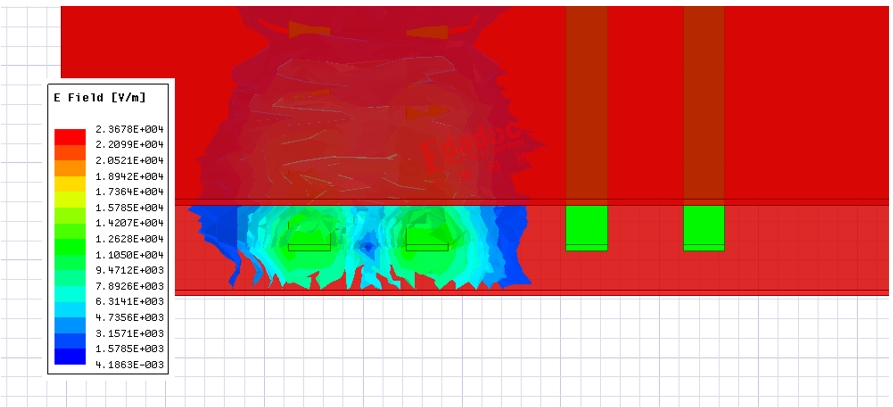

那首先我们看看只有一对走线的情况下,去仿真它的电磁场特性,结果如下:

可以看到,电磁场的范围基本上就在差分线中心往左边或者右边3H的距离,H是4mil。再远的地方其实就没太多电磁场分布了。从参考地平面的角度去看也是类似的结论,如下所示,也还是基本集中在3H的范围。

当然如果把另外一对做到3H原则的差分线一起放进来看,也能有同样的结论,左边这对攻击线的电磁场其实还没波及到右边这对受害线上面去。既然电磁场没波及过去,也就说明其实串扰能量也不会很多的传递过去。

Chris从电磁场的角度给设计的同事去分析,他们的确是有一种get到新知识的新鲜感,而且这个场的仿真结果也比较形象,能直观的看到“3H”设计原则的效果,他们看到都纷纷表示。。。赞!

当然,场的仿真结果其实也还是个定性的结果了,可能给PCB设计的同事看比较直观,但是并没有起到一个量化的效果。如果要量化具体指标的话,还得回到传统的S参数仿真方法,也就是直接进行串扰的频域仿真。

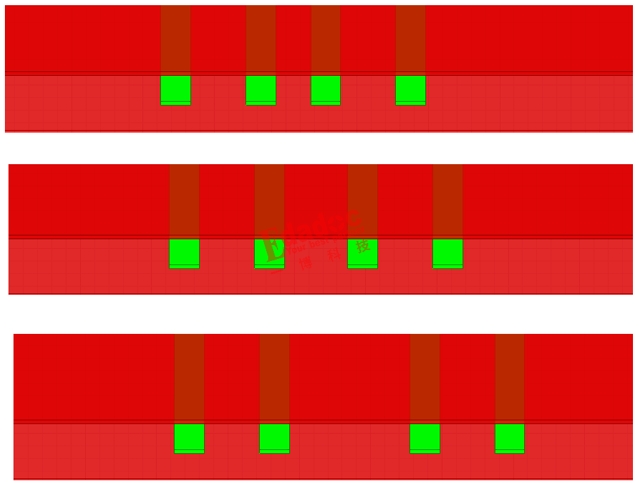

Chris对模型赋上一定的扫描变量,看看这两对差分线从最小的“2H”到“3H”再到“5H”(其实Chris还顺带偷偷仿真了“7H”哈)的情况下串扰具体数量的差异!以下就是“2H”、“3H”和“5H”三种case的仿真模型。

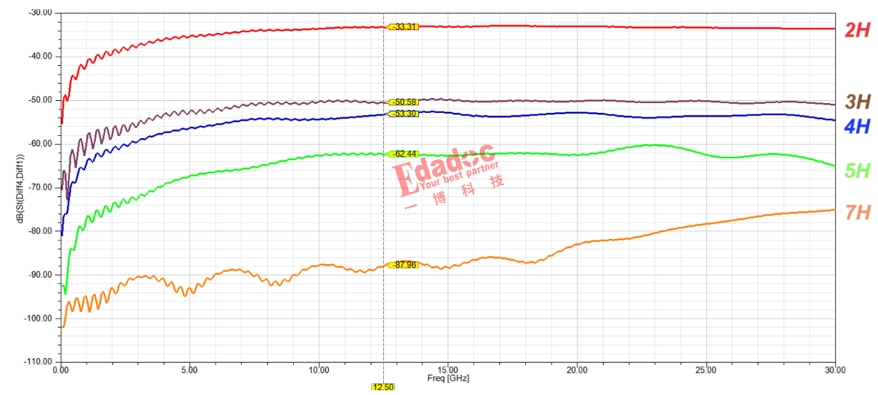

唰一下,不同差分线间距的串扰仿真结果都完成了,我们把结果放到一起来直观的对比,如下所示:可以看到,2H的情况下串扰就比较大了,只有不到35db,3H的话已经能做到50db,4H和3H其实差异就不大了,如果要往60db去做的话,就要达到5H的距离,如果继续追求高指标的话,7H可能是你们喜欢的设计哈!

当然对于25Gbps信号来说,编码方式是NRZ编码,其实3H是够用的了。如果在同样基频下要跑到56Gbps-PAM4的话,可能需要往5H做,因为PAM4的串扰的要求还是比较高的。反正需要做到多少间距,一个是看你们的产品的速率来定,另外就是看设计工程师能不能做到了哈。

当Chris把这个量化的S参数结果做出来准备再给设计部的同事展示的时候,发现他们早就跑光了,全部回去继续做他们的设计去了,对于设计工程师来说,知道原理和定性的看到电磁场的结果,他们其实已经满足了……